计算机组成原理背诵笔记

本文是西交折磨水课计组的复习背诵笔记,用的是王换招老师的课本。

考试回忆

都是 PPT 题型

- (10)填空:五空,八股;

- (15)简答:三题,八股,考了总线控制啥的;

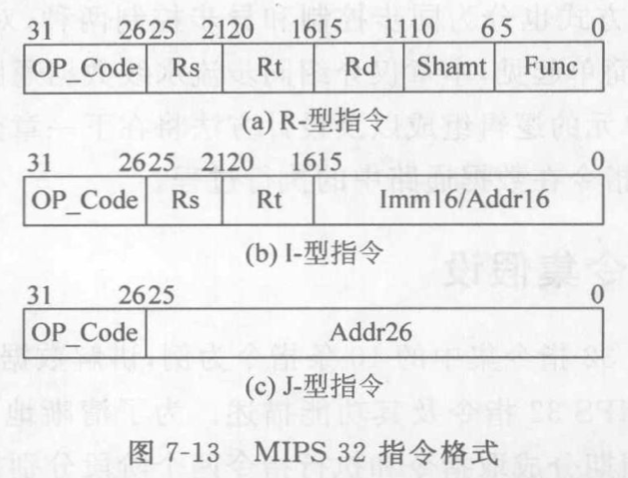

- (15)指令系统设计:写出格式、算各寻址方式的范围;

- (15)磁盘:大小、传输率计算等;

- (15)存储器设计:字位扩展、画连接图;

- (15)浮点运算:十分简单的加减;

- (15)双总线 CPU:判断未标明模块是什么(是

SigExt),写 ADD 指令周期。

Misc

常用进制/幂次对照

\(2^6=64=40H\)

\(2^{8}=256=100H\)

\(2^{10}=1024=400H\)

\(2^{13}=8192=2000H\)

Mega \(10^6\sim2^{20}\)

数电

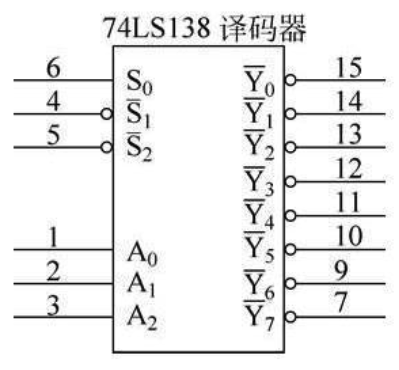

74LS138(3-8 译码器):\(S_0\) 为真,\(S_1\) 与 \(S_2\) 为假时工作(可能有低输出)

反向开悟

硬件:组成计算机的各种实际装置;软件:各类特殊功能的程序和相关数据(相互依存,逻辑上等价、协同发展)

层次结构:每层的结构:广义语言、解释器、作用对象

子学科

- 系统结构:主要研究计算机系统中软件和硬件的功能分配,以及确定软件和硬件的界面(现代计算机的发展主要是体系结构的变革)

- 组成:指计算机内部的逻辑组成和逻辑实现,各部件间的连接、通信、控制方式,以及信息的流动方式

- 实现:是对计算机组成的物理实现。研究各部件的物理结构、机器制造技术和工艺等

计算机分类:(信息表现形式和处理方式)数/模/混;(用途)专用/通用;(配置)巨/大中/小/微/工作站/服务器

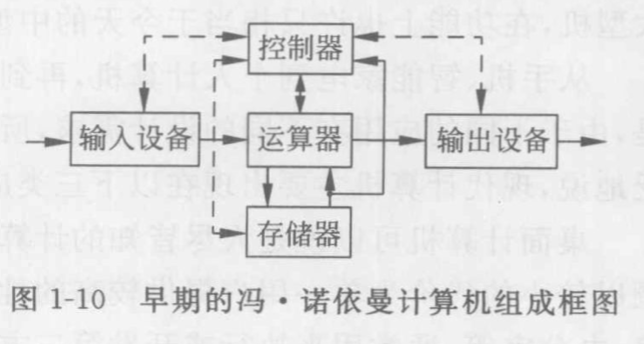

冯诺伊曼存储程序计算机:运算器、控制器、存储器、输入设备和输出设备

总线结构:片内总线、系统总线等

存储器:主存储器是计算机的主要工作存储器,存放正在运行的程序和数据;主存包括存储体、各种逻辑部件及控制电路等;存储单元(具有特定存储地址的存储单位);存储元

字长:CPU 能同时处理的最大数据位数(数据通路宽度,寄存器位数)

ISA

指令系统是指一台计算机所具有的全部机器指令的集合,它反映了该机所拥有的基本功能;机器语言;软硬件界面;指令系统的逻辑实现

RISC 特点:长度固定、LW SW 访存、GPR 多、流水线、硬布线控制

设计原则:完备性、规整性、高效性、兼容性

数据类型(应用或软件处理的数据结构);数据表示(硬件能够直接识别,指令能直接操作的数据类型);操作数(指令中的数据:地址、数字、字符、逻辑数)

地址空间(统一编址/单独编址)(按字编址/按字节编址)

大端(高字节低地址)(符号位永远最低)

小端(低字节低地址)(强转不换位)

指令类型:数据传送指令;数据运算指令;程序控制指令;输入输出指令;其他指令

CPU 结构:堆栈结构;累加器结构;通用寄存器 RS 型;通用寄存器 RR 型

地址码个数:(三二一零)地址指令

操作码扩展技术:当采用等长指令字格式,且多种地址码结构混合使用时,可利用地址码个数较少的指令空出的地址码字段,来增加操作码的位数

寻址方式(实际地址 EA)

指令寻址方式

顺序指令寻址(

PC=(PC)+1)跳跃指令寻址(存储器寻址)

数据寻址方式

基本寻址方式(立即寻址、寄存器寻址、存储器寻址、堆栈寻址)

- 存储器寻址:直接

A、间接(A)、寄存器间接(R)、偏移(相对(PC)+A/基址(Rb)+A/变址A+(Rx))、段(DS)<<4+(Rx)+A

- 存储器寻址:直接

复合寻址方式(变址间接、间接变址等)

程序定位方式:直接定位方式、静态定位方式、动态定位方式

存储器

按作用分类:内部存储器、外部存储器、控制存储器

按存储介质分类:半导体、磁表面、光盘

按存取方式分类:随机存取、只读、顺序存取(磁带)、直接存取(磁盘)、相联

按工艺分类:双极型、MOS 型

按可保存性分类:电易失型、非电易失型

RAM 的分类:SRAM; DRAM; NVRAM (SRAM+EEPROM)

层次原则:包含性、一致性

RAM/ROM

地址译码:

线选法 \(n\) 位地址译码线与驱动数 \(2^n\)

重合法(双译码)\(n\) 位地址译码线与驱动数 \(2^{n/2+1}\)

存取时间:一次存储器操作到完成的时间

存取周期:连续两次独立操作的最小间隔

存储器带宽:存取周期的倒数

引端名:电气引脚、逻辑引脚(数据线 \(D_i\)、地址线 \(A_i\)、控制线(读/写控制 \(\overline{WE}\)、片选控制 \(\overline{CS}\)))

SRAM 8 管(4 Latch;4 I/O 两高两低)

DRAM 3/1 管(\(C_g\) 电容状态),测位线电流,再生放大器;行列地址分时输入(\(\overline{RAS}\)(兼任片选)、\(\overline{CAS}\))

DRAM 刷新

集中式刷新:每个最大刷新间隔停下来逐行干一次

分散式刷新:每个读写周期刷一行

异步式刷新:分散每行的刷新

DRAM 类型

FPM DRAM(Fast Page Mode)快速页面模式:后续行地址省略

EDO DRAM(Extended Data Out)扩展数据输出:地址数据部分并行

SDRAM(Synchronous):与时钟同步

DDR SDRAM:上下沿都搞

DRAM 控制器(DRAMC)

刷新地址计数器

地址多路选择器:选通行、列、刷新地址

刷新定时器

仲裁电路(仲裁访存、刷新)

定时发生器(\(\overline{RAS}\),\(\overline{CAS}\),\(\overline{WE}\))

ROM

MROM(Mask ROM):造的时候就写好了

PROM(Programmable):溶丝式/反向二极管式

EPROM(Erasable):浮动栅极雪崩注入式 MOS(FAMOS),擦除需要特殊手段(紫外)

EEPROM(Electrically Erasable):浮动栅极上有控制栅

Flash:和 EEPROM 类似,但浮栅的绝缘层更薄,快,耐损耗性差

容量扩展技术

位扩展:总片数=字长/片字长;横向排列

字扩展:总片数=字数/片字数(加片选译码器);垂直排列

8086 内存接口:地址总线 20 位,数据总线 16 位,\(\overline{BHE}\) 信号和 \(A_0\) 决定高低字节;\(\overline{MREQ}\)(Memory request)

Cache

相连存储器

- 存储元是一个 D 触发器;未被 M 屏蔽时存储位与检索位 D 同或(屏蔽高阻)得匹配标志 P;字选线 S 控制数据位 Q 和写

- 按内容查找:检索/屏蔽寄存器-存储体-匹配寄存器-优先排队电路-存储体-数据输出

- 按地址查找:屏蔽码全零,输出 AE 低电平

Cache

命中率 \(H=N_1/(N_1+N_2)\)

失效率 \(F=1-H\)

平均访存时间 \(T_a=HT_c+(1-H)T_m\)

加速比 \(S_p=T_m/T_a\)

访问效率 \(e=T_c/T_a\)

区号 E;组号 G;组内块号 B;(块内地址 W)

全相连:全映射;直接相联:单射;组相连:块分组组内全相联

替换算法:RAND,FIFO,LRU,LFU(最不经常使用)

命中写回一致性:写直达法,写回法(替换时写,简单写回/标志位写回)

不命中写回一致性:不按写分配(写时不取),按写分配(写时取)

辅助存储器

软磁磁头、硬磁介质

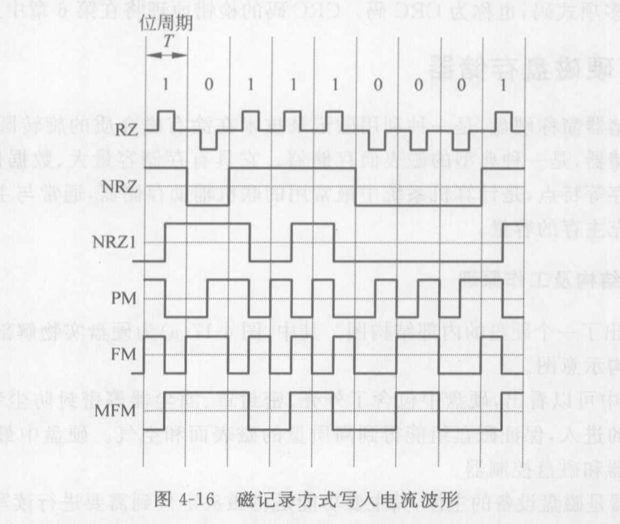

编码方法

归零(RZ):正负0

不归零(NRZ):正负,变化时反向

不归零 1(NRZ1):翻转沿为 1

调相(PM):周期中心点上跳为一,下跳为零,连续则在周期交界翻转

调频(FM):交界处翻转,写一中心点翻

改进调频(MFM):写一中心点翻,写零交界处翻

编码效率(密度与翻转次数之比):FM/PM 0.5,其他 1

自同步:RZ/PM/FM/NFM

每张盘片上下两面,一般最上最下不用;

磁道(磁头径向运动维+盘片维);地址:柱面、盘面、扇区

硬分区/软分区(0索引)

不定长记录格式:数据块大小可变

格式化磁盘容量 = 硬盘个数x磁盘记录面数x磁道数x每道扇区数x扇区容量

平均寻址时间 = 平均寻道时间+平均等待时间

内部数据传输率 = 磁道容量x转速;外部数据传输率:总线和缓冲区速率

总线和 IO

总线

系统总线:计算机单机系统内部各大部件间信息传输的公共通路

通信总线:计算机系统间或计算机与其他系统间的信息通路

按物理位置分:板级总线、板间总线

按信息分:数据总线、地址总线、控制总线

按传输方式分:串、并

总线控制:集中式、分布式

总线主模块、从模块

仲裁:链式查询、计数器定时查询、独立请求

链式查询:固定优先级优先链;三根信号线 BusRequest BusGrant BusBusy;BG 上游可掐断

计数器定时查询:地址计数,发出去地址匹配的模块可发

独立请求:每个模块独立 BR BG,控制器内部排队

一次总线操作:申请分配;寻址;传送;结束

总线周期:一次总线传送的时间(地址+数据);BURST(一次地址多次数据)

总线通信方式:

同步:公共时钟信号一致

异步:应答建立连接,周期可变

不互锁:发一段时间关,不管收

半互锁:主模块需 ACK,从不需

全互锁:均需 ACK

半同步:周期以快速为基础,对慢速部件加等待线

分离:Datagram,发的时候要发自己地址,准备好了再回

双总线结构:以 CPU 为中心(IO+存储)/以存储器为中心(系统+存储)

三总线结构:CPU 中心加 DMA 总线

总线特性:机械特性、电气特性、功能特性、时序特性

总线性能指标:宽度、频率、带宽、控制方式、通信方式、信号线数、负载能力、扩展能力

IO

编址:统一编址(访存即可);独立编址(IO 指令)

设备分类:人机交互设备、信息驻留设备、机机通信设备

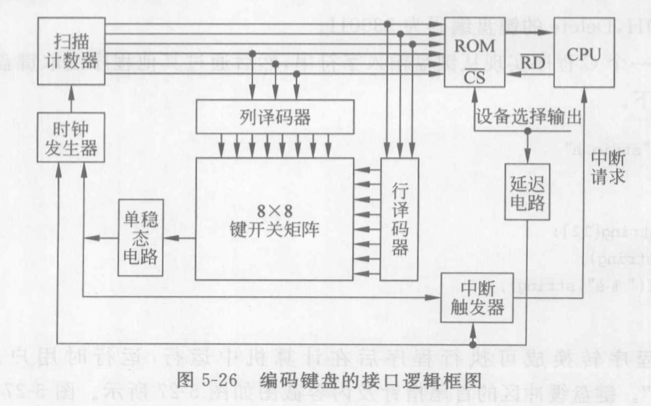

键盘

无编码键盘:扫描检查有无按键,程序查表编码

编码键盘:扫描检查有无按键,按键自动编码

显示器

字符、图形、图像显示器

CRT:光栅扫描、随机扫描(彩色 CRT 有三个阴极管)

刷新存储器 VRAM

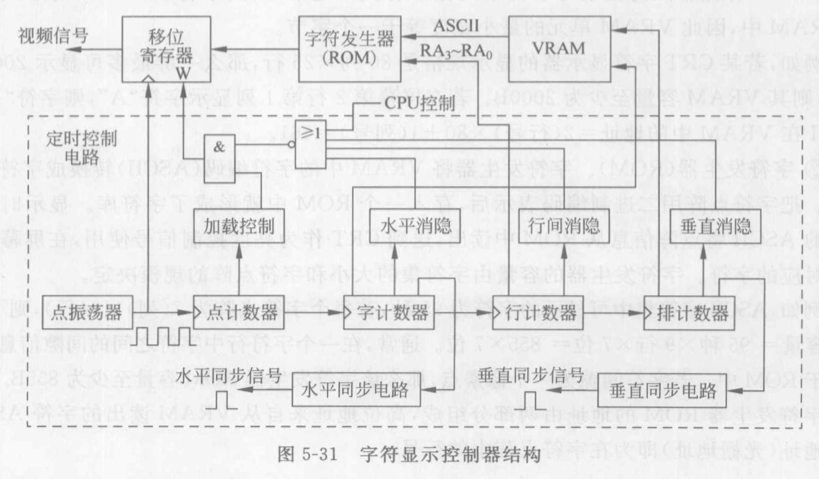

字符显示器

VRAM 地址 = 字符所在行号x一行字符数+列号

字符发生器 ROM

点振荡器(点时钟),点计数器(字符时钟),字计数器(行时钟),行计数器(排时钟),排计数器

打印机

和图形显示器一样

IO 接口

数据缓冲、串并转化、电气转换、控制、查询、寻址

组成:数据缓冲寄存器 DBR、设备选择电路、控制逻辑电路、设备状态标记、命令寄存器和命令译码器

同步异步;穿行并行

控制方式

程序查询(轮询)

中断:中断请求触发器 INTR,中断屏蔽触发器 MASK;中断允许触发器 INTA

中断判优:串行排队、并行排队

中断响应:关中断、保护断点、获得入口(软件查询、硬件向量)

中断服务:保护现场、中断处理、恢复现场

中断返回

中断嵌套:服务时开中断,优先级/屏蔽字(某中断可以屏蔽其他哪些)

DMA:预处理、传送、后处理

停止 CPU 访存;周期窃取;交替访存

选择型(并总线)、多路型(串优先)

I/O 通道

I/O 处理机

数据表示与数据运算

字符 ASCII,低 7 位,最高位恒为零/校验/扩展

汉字国标码/区位码

十进制 BCD:有权 8421;无权 余 3;自补 2421;循环 格雷码

定点小数(符号位后小数点)

数值数据表示

\(X\) 为真值;\(M\) 为最大值,定点整数为 \(2^n\),定点小数为 \(1\)

原码(仅设符号位)

\[ [X]_{原}=\begin{cases} X & 0 \le X < M \\ M-X & -M < X \le 0 \end{cases} \]

补码(负则反码加一)

\[ [X]_{补}=\begin{cases} X & 0 \le X < M \\ 2M+X \mod 2M & -M \le X < 0 \end{cases} \]

变形补码(两位符号位,特性与补码一致,可判溢出)

反码(全反,最高符号位,模是全一),符号位参与运算

移码(符号位相反的补码,便于比较,用于浮点指数)

\[ \begin{aligned} [X]_{移}=2^n+X & & -2^k\le X<2^k \end{aligned} \]

定点运算

全加器 \(X_i\), \(Y_i\),Carry \(C_i, C_{i+i}\),结果 \(F_i = X_i \oplus Y_i \oplus C_i\),\(C_{i+1}=X_iY_i+(X_i\oplus Y_i)C_i\)

加法溢出:同号相加变号;最高数值位和符号位进位不同;变形补码符号位不同

逻辑移位:补零;循环移位:补丢失数;算术移位:符号位不变,反码补 1

舍入:截尾;末尾置 1(或移出有一则置);0 舍 1 入

桶形移位器:32 选一

加法器

行波进位加法器:全加器串接

进位生成函数 \(g_i=X_iY_i\)

进位传递函数 \(p_i=X_i\oplus Y_i\)

进位 \(C_{i+1}=g_i+p_iC_i\)

先行进位表达式

\[ \begin{cases} C_1=g_0+p_0C_0 \\ C_2=g_1+p_1g_0+p_1p_0C_0 \\ C_3=g_2+p_2g_1+p_2p_1g_0+p_2p_1p_0C_0 \\ C_4=g_3+p_3g_2+p_2g_1+p_3p_2p_1g_0+p_3p_2p_1p_0C_0 \end{cases} \]

先行进位(CLA, Carry Look Ahead)

四位先行加法器:进位生成传递部件、CLA 部件、四位求和部件

成组先行——级连部件:组间串行进位

多级先行进位:\(C_{n+4}\) 由组间产生

小组进位生成函数 \(G_i=g_{n+3}+p_{n+3}g_{n+2}+p_{n+3}p_{n+2}g_{n+1}+p_{n+3}p_{n+2}p_{n+1}g_n\)

小组进位传递函数 \(P_i=p_{n+3}p_{n+2}p_{n+1}p_n\)

成组先行进位部件(BCLA, Block Carry Look Ahead)

\[ \begin{cases} C_{n+1}=g_n+p_nC_n \\ C_{n+2}=g_{n+1}+p_{n+1}g_n+p_{n+1}p_nC_n \\ C_{n+3}=g_{n+2}+p_{n+2}g_{n+1}+p_{n+2}p_{n+1}g_n+p_{n+2}p_{n+1}p_nC_n \\ G_{n}=g_{n+3}+p_{n+3}g_{n+2}+p_{n+2}g_{n+1}+p_{n+3}p_{n+2}p_{n+1}g_n+p_{n+3}p_{n+2}p_{n+1}p_ng_n \\ P_n=p_{n+3}p_{n+2}p_{n+1}p_n \end{cases} \]

4 位 BCLA 的 \(G_n\),\(P_n\) 输出给 4 位 CLA 输出进位 \(C_{4n}\)

二级先行——级连进位逻辑:大组串行进位

三级先行进位 \(G_n^*\),\(P_n^*\)

74181:4 位算术逻辑单元,有 CLA,BCLA 功能,可输出小组进位函数 \(P\),\(G\),组内进位不输出,输出求和信号

74182:4 位成组先行进位部件

进位延迟时间:设与非门延迟 \(t_y\),行波加法器 \(2nt_y\);假设与或非门延迟 \(1.5t_y\),先行进位 \(2.5t_y\),二级先行级连 \(10t_y\)

原码一位乘

设 \(X_s\),\(Y_s\) 为符号位,\(X^*\),\(Y^*\) 为绝对值,\(n\) 为非符号位位数

\[ P^*=\frac{1}{2}\left( X^*Y_1+\frac{1}{2}\left(X^*Y_2+\frac{1}{2}(\cdots)\right) \right) \]

结果是 \(2n\) 位,乘数右移时左侧容纳部分积,部分积带符号位防溢出

例:\(n=4\);\(X=0.1101\),\(Y=-0.1011\)

1 | Multiplicand |

补码一位乘法(比较法)

设 \([Y]_{补}=Y_0.Y_1Y_2\cdots Y_n\)

\[ Y=-Y_0+\sum_{i=1}^{n}2^{-i}Y_i=\sum_{i=0}^n2^{-i}(Y_{i+1}-Y_i) \]

\([XY]_{补}=[X]_{补}Y\)

部分积双符号位参加运算,乘数添一位零,最低两位判断位,加法系数 \(Y_{n+1}-Y_n\)

最后一次不移位,最低两位舍去,总移位次数为 \(n+1\),加法次数 \(n\)

例:\(X=0.1101\),\(Y=-0.1011\)

1 | Multiplicand |

对于整数,附加位后为小数点,最后一步运算右移两位,左去除多余符号位

例:\(X=1101\),\(Y=-1011\)

1 | Multiplicand |

补码二位乘法(比较法)

由一位乘法可得部分积

\[ [Z_{i+2}]_{补}=2^{-2}([Z_i]_{补}+(Y_{n-i+1}+Y_{n-i}-2Y_{n-i-1})[X]_{补}) \]

部分积三位符号位,乘数增加一位附加位,乘数增加符号位至偶数位,低三位清零

\(n\) 为奇数时,乘数设一位符号位,做 \((n+1)/2\) 次运算和移位,最后一次移一位

\(n\) 为偶数时,乘数设两位符号位,做 \(n/2 + 1\) 次运算,\(n/2\) 次移位

例:\(X=0.1101\),\(Y=-0.1011\)

1 | Multiplicand |

原码加减交替除法(不恢复余数法)

恢复余数法:每步试减,若余数小于零则加除数恢复余数再继续

对于恢复余数,可以直接下一步加,即 \(R_{i+1}=2(R_i-Y^*)+Y^*\);最后一步需要恢复余数,且余数不移位(共移位 \(n\) 次)

例:\(X=-0.1011\),\(Y=-0.1101\)

1 | Divisor |

浮点

\(N=MR^E\),\(M\) 为尾数,\(E\) 为阶码,\(R\) 为基底

阶码用移码表示

规格化:\(1/2<|M|<1\),即尾数最高位是有效值

机器零:尾数为零,阶码为最负(移码零)

IEEE754:隐藏位是一,移码偏移常数是 \(2^k-1\),符号位、阶码、尾数;单精度阶码 8 位,双精度 11 位

加法

- 检测零

- 对阶:求阶差,小阶尾数右移对齐

- 尾数运算:两位符号位判溢出

- 规格化:溢出右规,非规格化左归

- 舍入:零舍一入

- 溢出判断:上溢出错,下溢表零

乘除

- 检测零

- 阶码加减:移码需要修正偏置

- 尾数乘除

- 规格化

- 舍入

- 判溢出

CPU

五大功能:顺序控制、操作控制、时间控制、数据加工、中断控制

五个基本功能组件:算术逻辑单元、寄存器组、内部总线、中断系统、控制单元

数据通路:全部执行部件的集合

微操作:不可再分解的操作;微命令:执行微操作所需要的控制信号

中断系统

- 允许中断

EINT,中断请求INTR_i - 指令周期结束后响应中断

- 外部中断源:中断控制器;内部中断源

- 中断判优:软、硬件

- 中断响应

- MIPS:出错地址

EPC,原因Cause,中断服务由操作系统提供

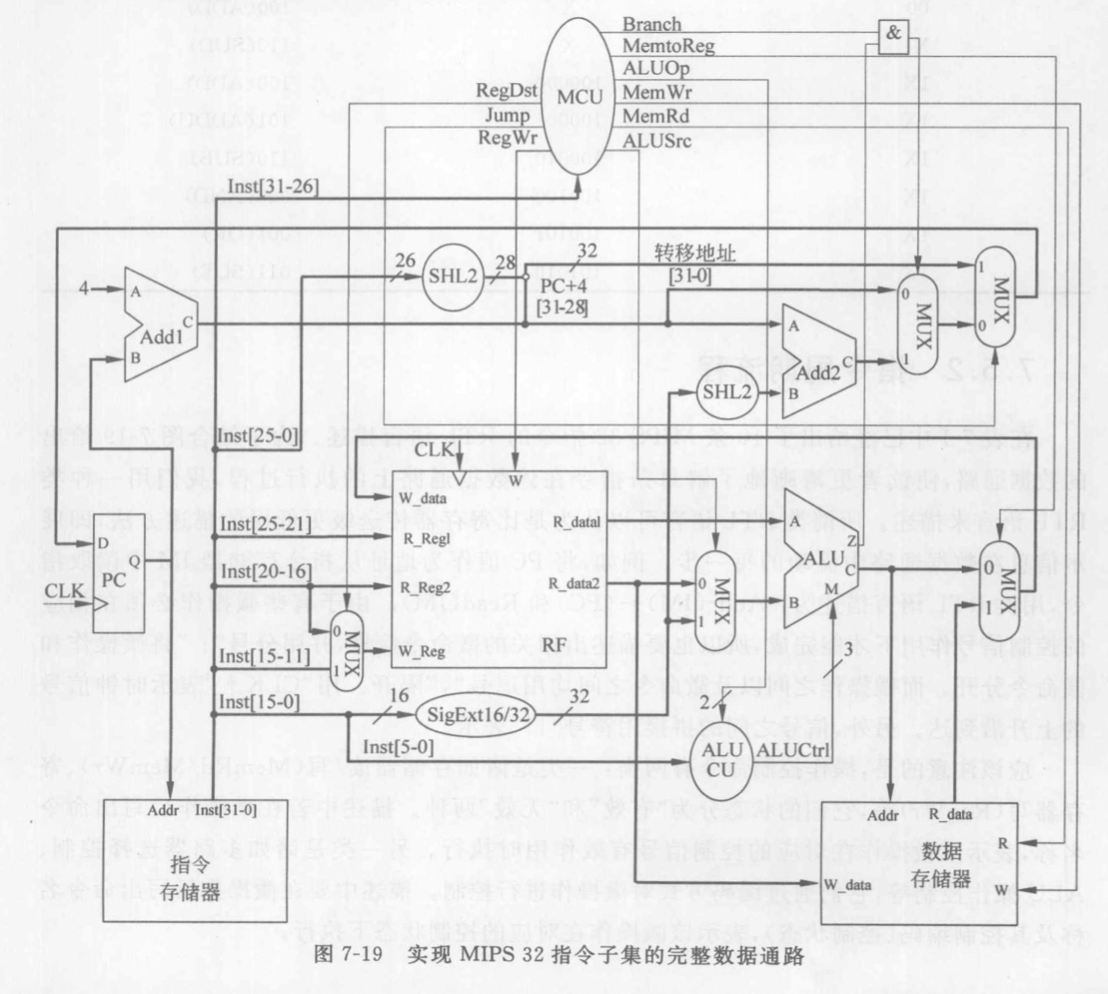

单周期数据通路

组成

- 指令存储器

IM - 数据存储器

DM - 程序存储器

PC - 寄存器组

RF - 算术逻辑单元

ALU - 加法器(PC+4)

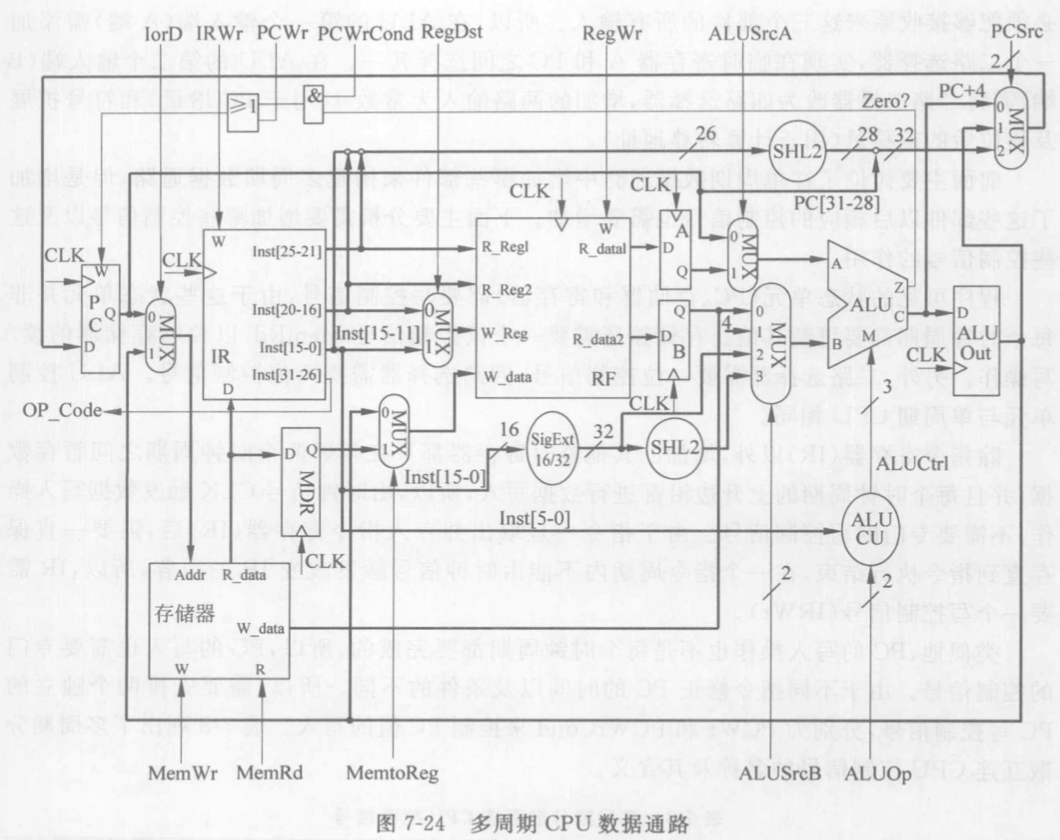

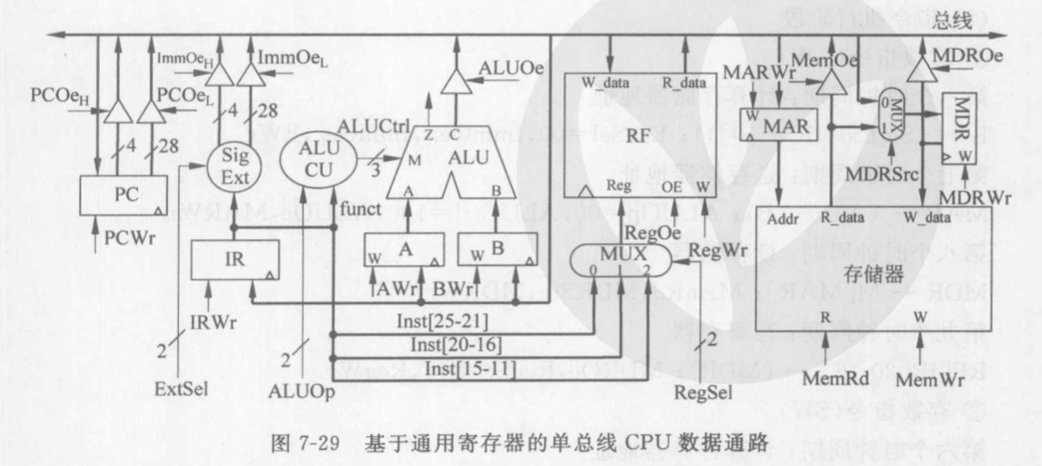

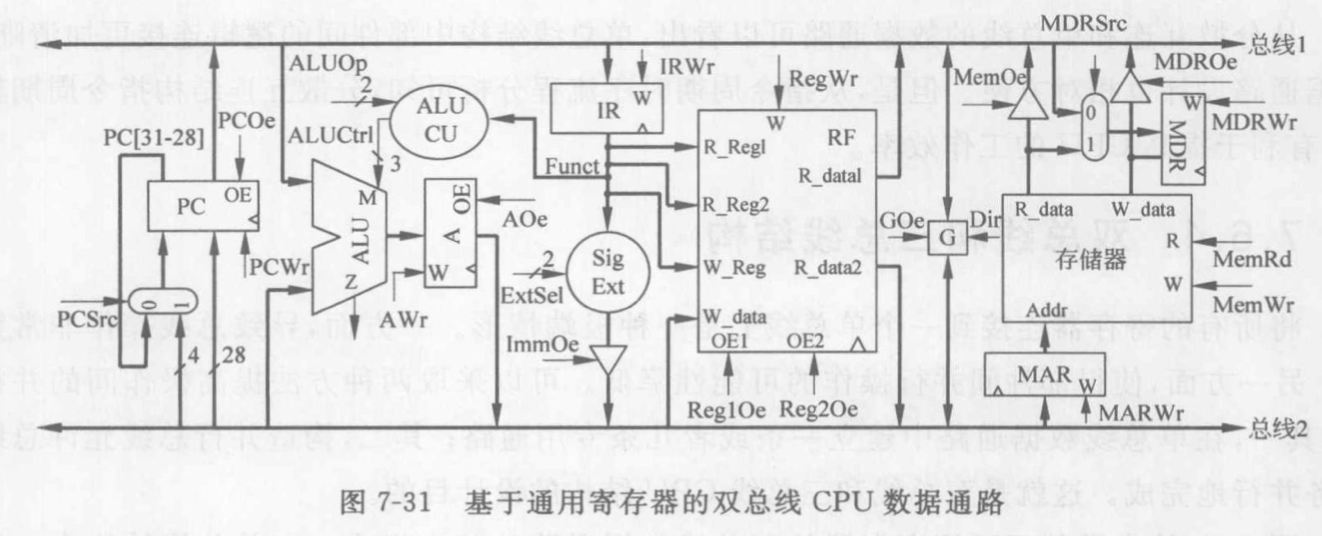

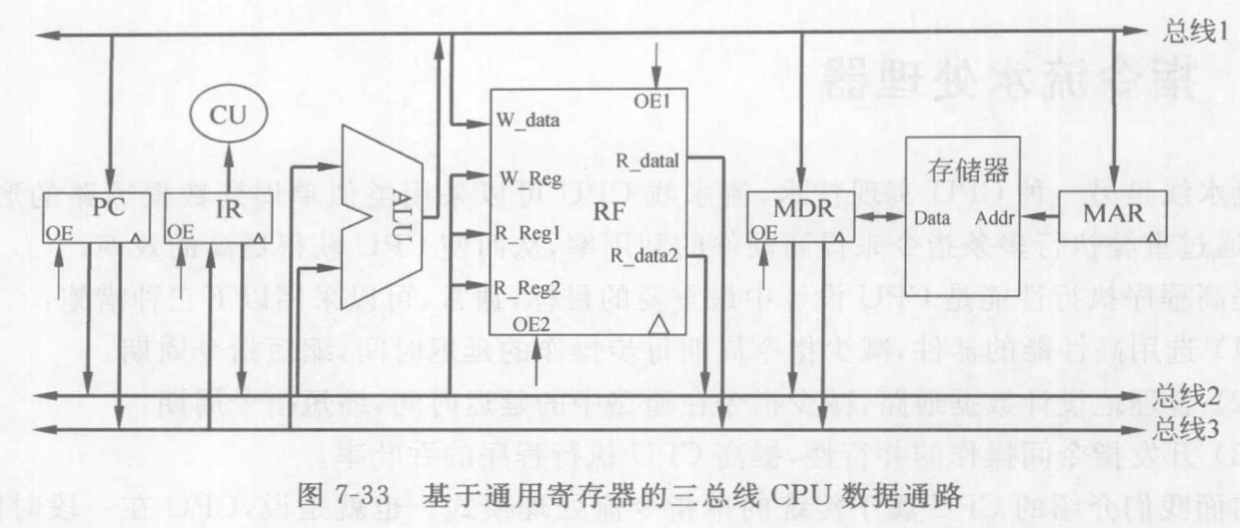

多周期数据通路

分散互联:合并冗余单元(指令数据存储器,加法器和 ALU);增加

IR,MDR,A,B,ALUOut

寄存器

单总线:增强符号扩展器的功能(SigExt(IR[15-0])、SigExt(IR[15-0])<<2、4、IR[25-0]<<2)

转移指令将 26 位地址左移两位与 PC 高四位拼接

取指令阶段

1 | RTL Ctrl |

ADD

1 | RTL Ctrl |

LW

1 | RTL Ctrl |

双总线

三总线

性能

指令的 CPI 按频度加权平均

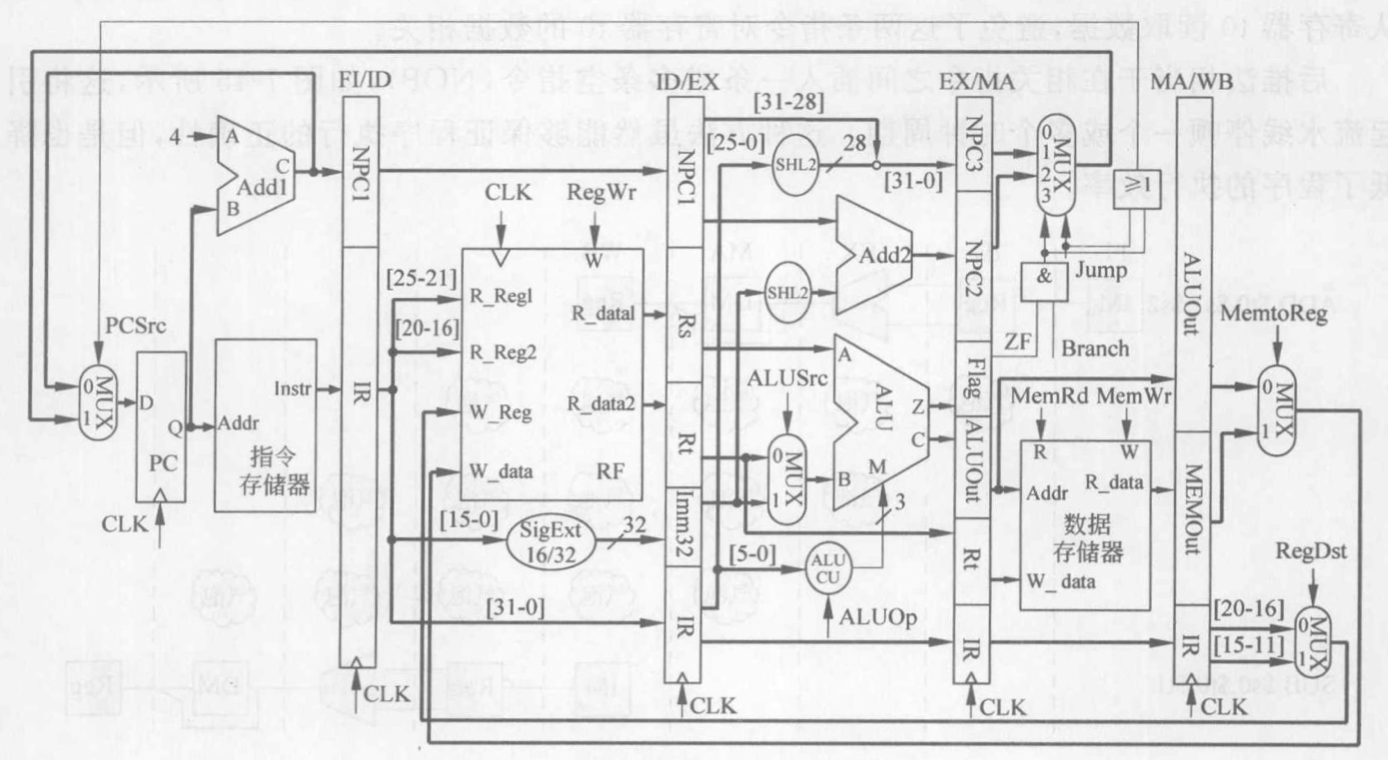

流水

部件冗余、数据冒险、控制冒险、吞吐率、加速比、效率

五级:FI、ID、EX、MA、WB

控制器

作用:提供定时信号、提供控制信号、响应中断请求

组成:控制寄存器、译码器、时序信号产生器、CU

组合逻辑控制器,微程序控制器,混合设计

三级时序体制:主状态周期;节拍电位(多个传送操作);节拍脉冲(同步控制信号)

控制方式:同步(时序信号触发状态转移);异步(握手机制触发转移)

- 同步控制方式:统一、不定长、中央局部

- 异步:二级时序(节拍、脉冲)

- 联合

硬布线控制器 \(C_i=f(I_m, B_j, M_l, T_k, P_n)\),是译码信号、机器状态、机器周期、节拍和脉冲的函数

门阵列控制器:用门阵列芯片实现

多周期同步控制单元:组合逻辑和状态寄存器

SR;异步:加一个 Ready 信号

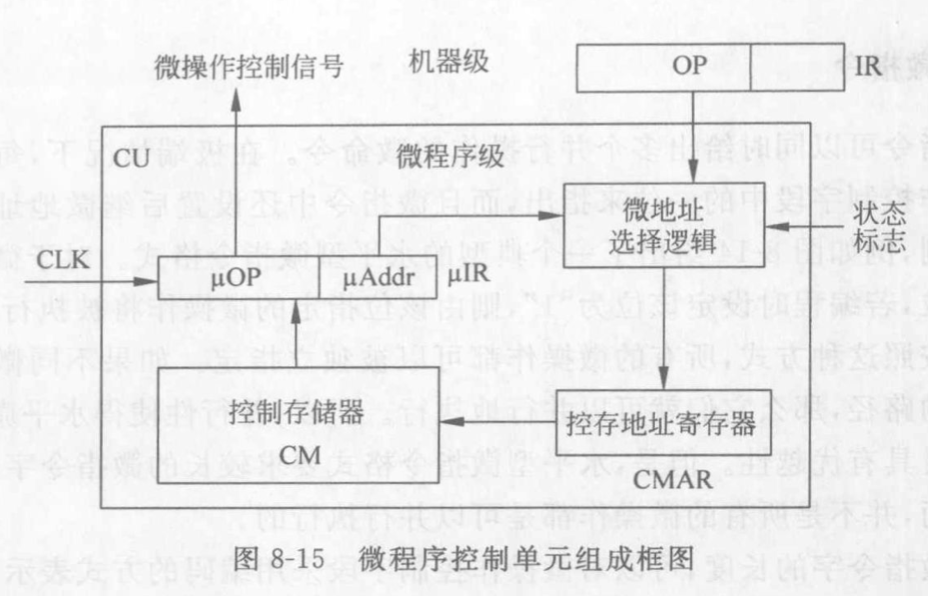

微程序

微指令格式:微操作控制字段

uOP(能产生微命令);顺序控制字段

uAddr(下一条控存地址)

水平型微指令:一条微指令多个微命令;垂直型微指令:不多个微指令

编码方法

- 直接编码(不译)

- 字段直接编码:互斥命令组织编码

- 字段间接编码:某些微命令要由其他字段解释

- 混合编码:直接编码和字段直接编码混合

微地址形成方法

- 直接表示:下一条

- 增量方式:CMAR 增加计数功能;分顺序微指令和转移型微指令(条件(转或顺序)、转移地址)

- 增量与下址字段相结合方式:对比增量方式没有顺序微指令

- 断定方式:非测试地址字段,测试条件字段(可以多路转移)

微入口技术:解决如何进入相应微程序,“功能转移”,查表法、转移地址产生逻辑

微指令周期(微周期):取,执行;串行:先取再执行;重叠:执行和取并行